计算机组成原理(第3版)唐朔飞著 知识点总结 第四章存储器

其他章内容在这里

汇总链接

第四章 存储器

一、 存储芯片

-

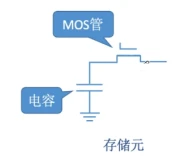

一个存储体由多个存储单元构成,存储单元由存储元构成。直接存放二进制数据

-

MOS管理解为电控开关,电压达到某阈值时接通

-

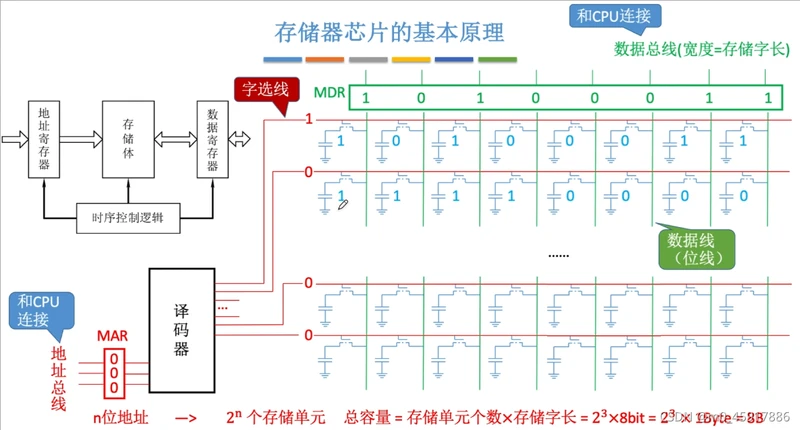

每一个地址对应译码器的一根字选择线

地址寄存器与数据寄存器和存储体共同作用于时序控制逻辑电路

存储字长不是确定值

-

-

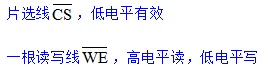

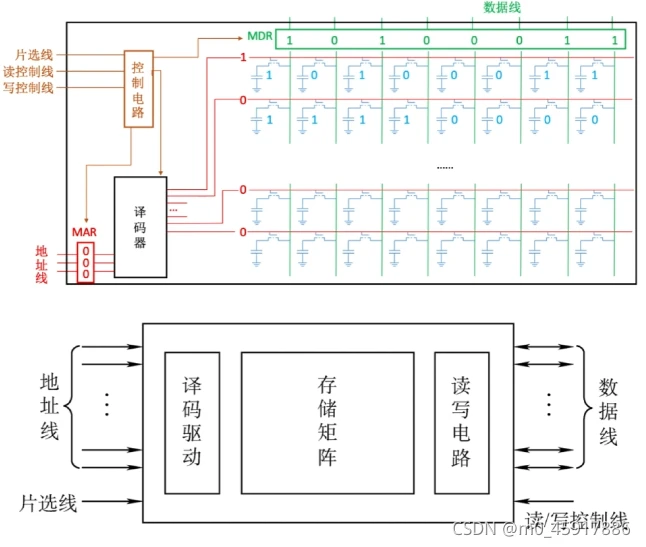

译码驱动由译码器与驱动器组成。驱动器接在译码器后保证译码器的高电平是稳定有效的

-

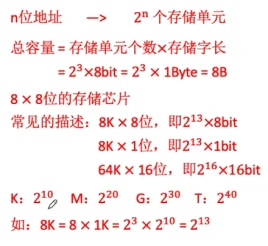

存储芯片的描述 【Byte为字节=8bit为位】

-

技术性能指标

1 存储容量

2存储速度【存取时间 存取周期】

3 存储带宽 -

例: 一个64Kx8位的存储器可由32片16Kx1位的存储芯片组成

解析:(64K8)/(16K1) = 32片

1位代表存储字长为1bit,所以将其先转化成16Kx8位

16与64相差4倍,通过译码器再增加两根地址即可表示

所以最终需要48 = 32片* -

半导体存储芯片的译码驱动方式有两种:线选法和重合法

-

线选法占用太多线路:通过一根线获取水平方向一行的数据

-

重合法容量可以很大:行列交叉位置的数据

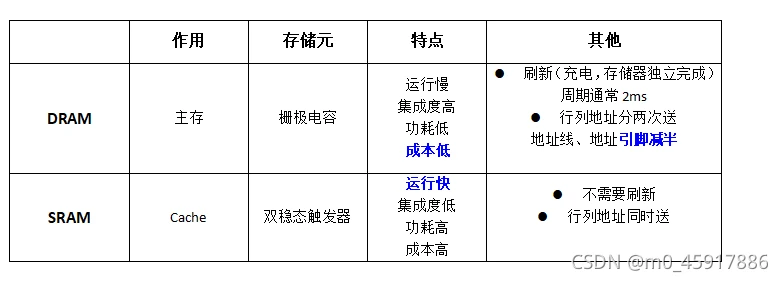

二、RAM(DRAM和SRAM)

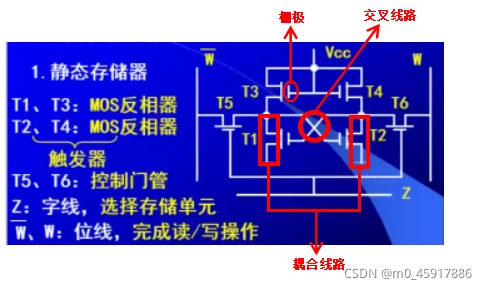

- SRAM:静态RAM(双稳态触发器原理)

【短杠上只连接一根线的位置叫做栅极,给栅极高电平即可导通】

T1-T4组成了一个触发器

T5、T6:控制门管(若T5、T6被断开内部则无法选中)

Z:字线(选择存储单元)

(通过控制位线电平,来控制写入状态)

T1导通,T2截止 写1

T1截止,T2导通 写0

(通过读取位线电流,来读取状态)

位线1有电流,位线2无电流 读1

位线2有电流,位线1无电流 读0

写步骤(此时有电压差走交叉线路):

① 字线给高电平(T5、T6都导通)

② 根据要写入的状态给两位线不同电平(H高L低)

读步骤(此时无电压差走耦合线路) :

① 字线给高电平(T5、T6都导通)

② 两位线都给高电平

③ 检测电流

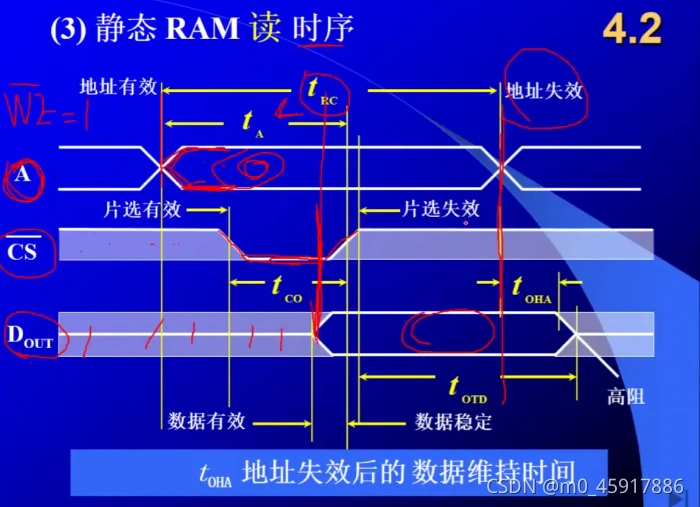

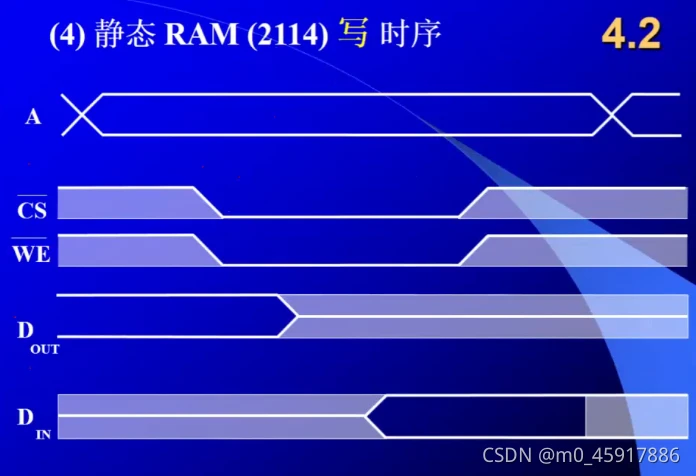

- 静态RAM的读写时序

- 读出的时候地址信号和片选信号必须稳定

- 读出的过程中地址信号和片选信号可以发生变化

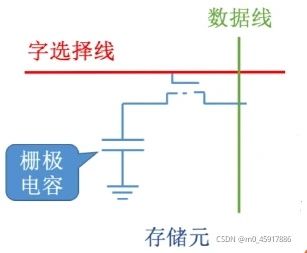

- DRAM:动态RAM(栅极电容)集成度高、功耗低

读1:MOS管接通,电容放电,数据线上产生电流(电容放电是破坏性读出,还需重写操作)

读0:MOS管接通后,数据线上无电流

地址送两次,一次行地址,一次列地址

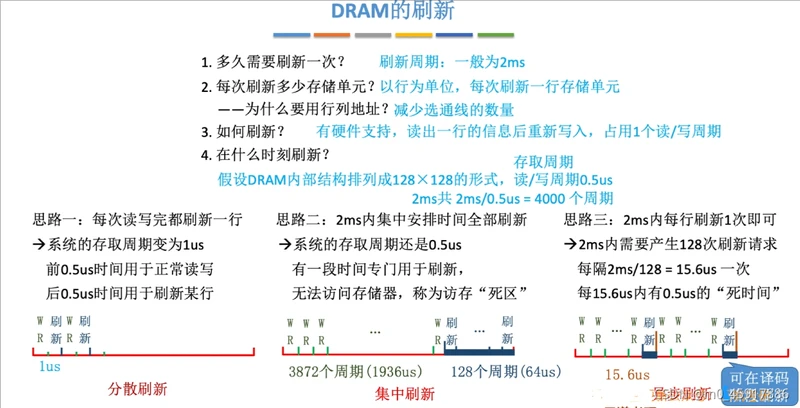

- 刷新

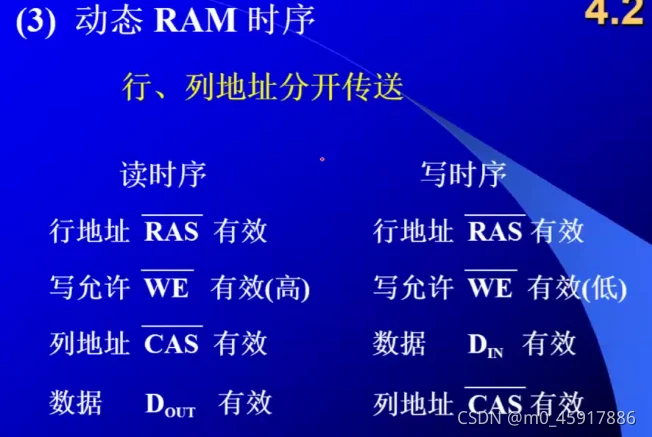

- 动态RAM的读写时序

三、ROM

1. 五种ROM

-

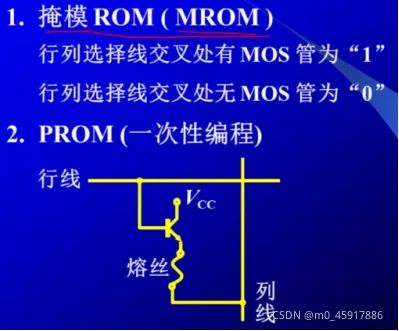

掩模ROM(MROM)

-

可编程ROM(PROM)(一次性编程)

熔丝连接为1,断开为0

-

EPROM(多次编程,紫外线擦除)

-

EEPROM(电可擦除存储器)

-

闪速存储器

2. 存储器与CPU的连接

- 存储器容量的扩展

1. 字扩展(地址线)

多个芯片的片选端,连接到扩展的地址线上

解释:多个芯片不能同时工作

2. 位扩展(数据线——增加存储字长)

各个存储芯片的片选线连在一起

解释:数据位扩展,多个芯片要同时工作,所以片选线要连在一起

3. 字位扩展

先扩展位,再扩展字。

扩展的位相当于分好了列,扩展后的位数为一组,同一组的芯片片选线连到一起

把这几组的片选线,连接到扩展的地址线上(片选译码器分出多个信号)

四、校验

1.奇偶校验

- 奇偶校验(高位放一位校验码)不能指出错误

加上最高位,1的个数是奇数个是奇校验,1的个数是偶数个是偶校验

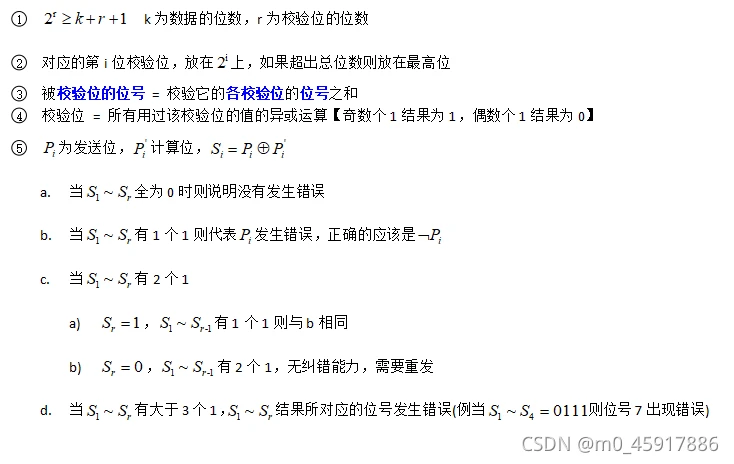

2.海(汉)明码校验

- 海(汉)明码校验

五、Cache

1.块号、块内地址

主存:

块号 | 块内地址

块数 容量(块长)

Cache:

块号 | 块内地址

远小于主存 容量与主存一样

2.写Cache:

(1)写直达法:

优:始终保持一致

缺:增加访存次数

(2)写回法:

优:快

缺:成本高(增加的电路多)

3.Cache映射:

(1)直接映射:

优:直接简单

缺:利用率低,命中率低

(2)全相联映射:

优:资源利用自由

缺:成本高

(3)组相联映射:

先分组(直接映射)

后选块(全相联映射)